## Macroelectronic Integrated Circuits Using High-Performance Separated Carbon Nanotube Thin-Film Transistors

Chuan Wang,<sup>§</sup> Jialu Zhang,<sup>§</sup> and Chongwu Zhou\*

Department of Electrical Engineering, University of Southern California, Los Angeles, California 90089, United States. <sup>S</sup>These authors contributed equally to this work.

ingle-walled carbon nanotubes offer extraordinary electrical properties<sup>1-5</sup> such as high intrinsic carrier mobility and current-carrying capacity and have already been used extensively to demonstrate ballistic and high mobility transistors<sup>6-8</sup> and integrated logic circuits such as inverters and ring-oscillators.9-13 Thin-films of single-walled carbon nanotubes which possess extraordinary conductivity, transparency, and flexibility have been achieved using either solution-based filtration or chemical vapor deposition (CVD) methods.<sup>14–21</sup> Compared with other popular channel material for thin-film transistors (TFTs), such as amorphous silicon<sup>22-24</sup> or organic materials,<sup>25-28</sup> nanotube thin-films have the advantages of room-temperature processing compatibility, transparency, and flexibility, as well as high device performance. Recently, CVDgrown nanotube thin-films have been used to demonstrate TFTs with outstanding electrical properties, and significant advance has been made toward flexible devices and integrated circuits.<sup>16,19,21</sup> Nevertheless, the mainstream nanotube TFT approach mentioned above shares one drawback which is the coexistence of both metallic and semiconducting nanotubes with approximate 33% nanotubes being metallic. For electronic applications, the problem of the coexistence of metallic and semiconducting nanotubes can be solved by using preseparated nanotubes with high purity semiconducting nanotubes.<sup>29,30</sup> Based on the separated nanotubes, TFTs have been demonstrated by the IBM research group using an evaporation self-assembly method<sup>31</sup> and our group using the solutionbased aminosilane-assisted wafer-scale separated nanotube deposition tech-

**ABSTRACT** Macroelectronic integrated circuits are widely used in applications such as flat panel display and transparent electronics, as well as flexible and stretchable electronics. However, the challenge is to find the channel material that can simultaneously offer low temperature processing, high mobility, transparency, and flexibility. Here in this paper, we report the application of high-performance separated nanotube thin-film transistors for macroelectronic integrated circuits. We have systematically investigated the performance of thin-film transistors using separated nanotubes with 95% and 98% semiconducting nanotubes, and high mobility transistors have been achieved. In addition, we observed that while 95% semiconducting nanotubes are ideal for applications requiring high mobility (up to 67 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>) such as analog and radio frequency applications, 98% semiconducting nanotubes are ideal for applications requiring high on/off ratios (> 10<sup>4</sup> with channel length down to 4  $\mu$ m). Furthermore, integrated logic gates such as inverter, NAND, and NOR have been designed and demonstrated using 98% semiconducting nanotube devices with individual gating, and symmetric input/output behavior is achieved, which is crucial for the cascading of multiple stages of logic blocks and larger scale integration. Our approach can serve as the critical foundation for future nanotube-based thin-film macroelectronics.

**KEYWORDS:** separated carbon nanotubes · thin-film transistors · purity of semiconducting nanotubes · integrated logic circuits · symmetric input/output · circuit design and optimization

nique.<sup>32</sup> In those previous reports, high performance separated nanotube thin-film transistors (SN-TFTs) have been demonstrated which exhibit on/off ratio of more than 10<sup>4</sup>, on-current density up to 10  $\mu$ A/  $\mu$ m, and mobility up to 50 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>. In spite of the significant progress, many interesting issues remain to be studied. For example, what are the key factors affecting the SN-TFT performance? Is there any tradeoff in terms of device performance when using separated semiconducting nanotubes of different purities? Can we assemble the SN-TFTs for integrated circuit applications?

To answer the above-mentioned questions, we report our recent advance on the application of high-performance SN-TFTs for macroelectronic integrated circuits. Our work includes the following essential components. (1) We have measured SN-TFTs \*Address correspondence to chongwuz@usc.edu.

Received for review August 24, 2010 and accepted November 01, 2010.

Published online November 9, 2010. 10.1021/nn1021378

© 2010 American Chemical Society

VOL. 4 • NO. 12 • 7123-7132 • 2010

with various channel lengths and widths, systematically compared the key performance metrics such as on-current density, on/off ratio, transconductance, and mobility of devices using separated nanotubes with 95% and 98% semiconducting nanotubes. From the comparison, we have observed that while 95% semiconducting nanotubes are ideal for applications requiring high mobility (up to  $67 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ ) such as analog and radio frequency applications, 98% semiconducting nanotubes are ideal for applications requiring high on/off ratio (>10<sup>4</sup> with channel length down to 4  $\mu$ m). This trade-off between the mobility and on/off ratio can serve as the guidance for SN-TFT device optimization for integrated circuit applications. (2) Integrated inverter design using SN-TFTs has been systematically investigated. Studies find that due to the highly uniform nature of our SN-TFTs, the integrated inverters can be readily designed using the conventional silicon field-effect transistor circuit design theory. By simply changing the dimensions of the switching and load transistors in the layout design, inverters with different voltage gains can be achieved and the measurement results are in consistence with the theoretical calculations. Moreover, these inverters with SN-TFTs exhibit symmetric input/output behavior, which allows the cascading of multiple stages of logic blocks and large scale integration. (3) In addition to inverters, more sophisticated logic circuits such as 2-input NAND and NOR have also been demonstrated. Our SN-TFT platform shows significant advantages over conventional platforms with respect to scalability, reproducibility, and device performance, and suggests a practical and realistic approach for nanotube-based macroelectronic integrated circuit applications.

## **RESULTS AND DISCUSSION**

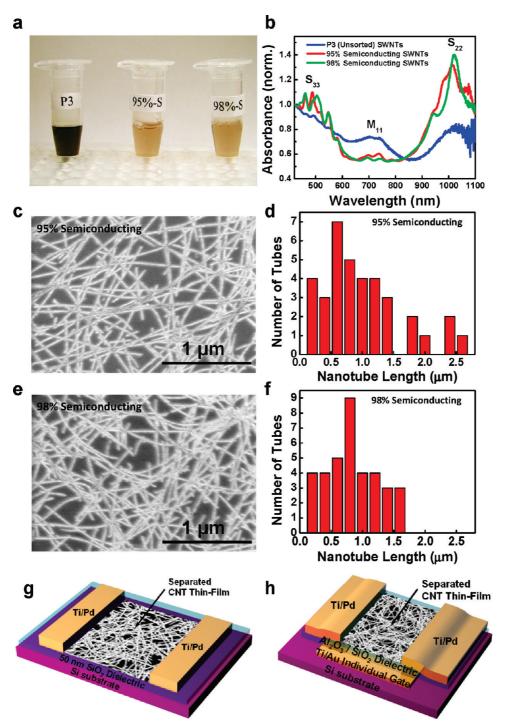

We have characterized the separated nanotubes with different purities of semiconducting nanotubes and compared them with the unsorted nanotubes with approximately 33% metallic nanotubes. Figure 1a is a photograph showing the unsorted arc-discharge P3 (Carbon solutions, Inc.) as well as 95% and 98% semiconducting single-walled carbon nanotube solution used in this study. The separated 95% and 98% semiconducting nanotubes (IsoNanotubes-S) were obtained from NanoIntegris, Inc. These samples were enriched by density gradient ultracentrifugation, where the chemical discrimination of surfactant molecules to adsorb on metallic or semiconducting nanotubes results in a density difference between metallic and semiconducting nanotubes. By repeating the same separation process, the purity of semiconducting nanotubes can be continuously improved. Figure 1b shows the UV-vis-NIR absorption spectra of the as-prepared P3 arc-discharge nanotubes (blue trace), 95% semiconducting separated nanotubes (red trace), and 98% semiconducting separated nanotubes (green trace).

Comparing those three traces, one can clearly see the enrichment of semiconducting nanotubes in the separated nanotube sample indicated by the decrease in  $M_{11}$  peak and increase in  $S_{22}$ ,  $S_{33}$  peaks.

To deposit high density, uniform separated nanotube thin-film onto the Si/SiO<sub>2</sub> substrates for device fabrication, we use the solution-based aminosilaneassisted separated nanotube deposition technique reported in the publications of Bao et al.<sup>33</sup> and in our previous publication.<sup>32</sup> Using this method, uniform nanotube networks are formed on top of the Si/SiO<sub>2</sub> substrates functionalized with aminopropyltriethoxy silane (APTES) (see Methods). Compared with the work we reported previously,<sup>32</sup> the nanotube network deposited here has higher density due to the optimized nanotube deposition recipe, which leads to improved device performance in terms of mobility as discussed below. Field-emission scanning electron microscope (FE-SEM) is used to inspect the samples after nanotube assembly and the SEM images of the 95% and 98% semiconducting nanotubes deposited on Si/SiO<sub>2</sub> substrates are shown in Figure 1 panels c and e, respectively. From the image, one can find that the samples with APTES functionalization give high density uniform nanotube deposition throughout the sample. The average nanotube density for the 95% semiconducting nanotubes is measured to be 41 tubes/ $\mu$ m<sup>2</sup> and the average nanotube density for the 98% semiconducting nanotubes is measured to be 46 tubes/µm<sup>2</sup>. Information about the deposition uniformity throughout a 3 in. wafer can be found in our previous publication.<sup>32</sup> The length distribution of the 95% and 98% semiconducting nanotubes are also characterized based on the SEM images, and the corresponding histograms are plotted in Figure 1d,f, respectively. The length of the 95% semiconducting nanotubes is measured to be 0.97  $\pm$  0.63  $\mu$ m, and the length of the 98% semiconducting nanotubes is measured to be 0.81  $\pm$  0.41  $\mu m.$

The deposited separated nanotube thin-films are used for the fabrication of back-gated SN-TFTs (see Methods) and individual-gated SN-TFTs (see Methods). The back-gated SN-TFT uses the highly doped silicon substrate as the gate and 50 nm SiO<sub>2</sub> as the gate dielectric and can be used as a simple platform for characterizing and comparing the electrical performance of the separated nanotube thin-films. On the other hand, the individual-gated SN-TFT has photolithography patterned Ti/Au gate where the individual gating allows the individual control of every transistor in an integrated circuits. The schematic diagrams of the back-gated and individual-gated SN-TFTs are shown in Figure 1 panels g and h, respectively.

We first use the back-gated SN-TFTs to directly compare the electrical performance of the 95% and 98% semiconducting nanotube thin-films. The nanotube deposition, devices fabrication for both nanotube samples are carried out at the same time so that any

ACSNANO

7124

Figure 1. Comparison of nanotubes separated by density gradient ultracentrifugation with different purities of semiconducting nanotubes: (a) photograph of P3 (unsorted), 95% semiconducting and 98% semiconducting single-walled carbon nanotube solution; (b) UV-vis-NIR absorption spectra of the as-prepared P3 arc-discharge nanotubes (blue trace), 95% semiconducting separated nanotubes (red trace), and 98% semiconducting separated nanotubes (green trace); (c) FE-SEM images of 95% semiconducting separated nanotubes deposited on Si/SiO<sub>2</sub> substrates with APTES functionalization, the average density is 41 tubes/ $\mu$ m<sup>2</sup>; (d) length distribution of the 95% semiconducting separated nanotubes. the average nanotube length is 0.97  $\mu$ m; (e) FE-SEM images of 98% semiconducting separated nanotubes deposited on Si/SiO<sub>2</sub> substrates with APTES functionalization, the average density is 46 tubes/ $\mu$ m<sup>2</sup>; (f) length distribution of the 98% semiconducting separated nanotubes, the average nanotube length is 0.81  $\mu$ m; (g) schematic diagram of a back-gated SN-TFT; (h) schematic diagram of an individual-gated SN-TFT.

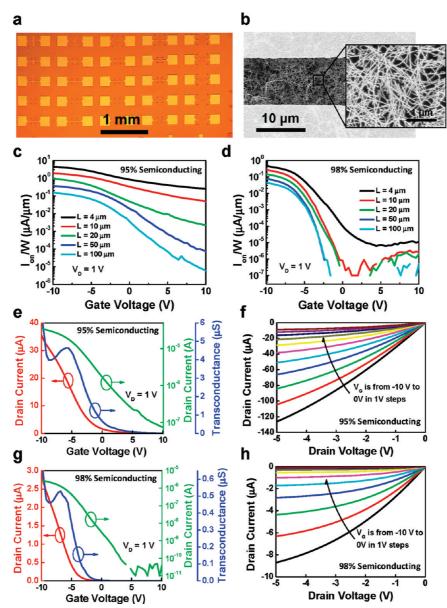

variation in the sample preparation and device fabrication process can be minimized. Such SN-TFTs are made with channel widths (*W*) of 10, 20, 50, 100, and 200  $\mu$ m, and channel lengths (*L*) of 4, 10, 20, 50, and 100  $\mu$ m. A microscope image of the fabricated SN-TFT array is shown in Figure 2a, and the SEM image of the channel of a typical SN-TFT with 10  $\mu$ m channel length is shown in Figure 2b.

## ARTICLE

7126

SNANO

Figure 2. Electrical properties of back-gated SN-TFTs using 95% and 98% semiconducting nanotubes. (a) Optical microscope image of the SN-TFT array fabricated on a silicon substrate with 50 nm SiO<sub>2</sub> acting as gate dielectric. (b) FE-SEM image showing the channel of a typical back-gated SN-TFT with 10  $\mu$ m channel length. (c, d) Transfer characteristics ( $I_D-V_G$ ) of the SN-TFTs using 95% (c) and 98% (d) semiconducting nanotubes with various channel lengths (4, 10, 20, 50, and 100  $\mu$ m) and 100  $\mu$ m channel width plotted in logarithm scale. (e) Transfer characteristics (red, linear scale; green, log scale) and  $g_m-V_G$  characteristics (blue) of a typical SN-TFT ( $L = 50 \ \mu$ m,  $W = 100 \ \mu$ m) using 95% semiconducting nanotubes. (f) Output characteristics ( $I_D-V_D$ ) of the same device in panel e. (g) Transfer characteristics (red, linear scale; green, log scale) and  $g_m-V_G$  characteristics (red, linear scale; green, log scale) and  $g_m-V_G$  the same device in panel e. (g) Transfer characteristics (red, linear scale; green, log scale) and  $g_m-V_G$  the same device in panel e. (g) Transfer characteristics (red, linear scale; green, log scale) and  $g_m-V_G$  the same device in panel e. (g) Transfer characteristics (red, linear scale; green, log scale) and  $g_m-V_G$  the same device in panel e. (h) Output characteristics (red, linear scale; green, log scale) and  $g_m-V_G$  the same device in panel e. (h) Output characteristics (red, linear scale; green, log scale) and  $g_m-V_G$  the same device in panel e. (h) Output characteristics (red, linear scale; green, log scale) and  $g_m-V_G$  the same device in panel e. (h) Output characteristics (red, linear scale; green, log scale) and  $g_m-V_G$  the same device in panel e. (h) Output characteristics (h) panel e. (h) output characteristics (h) panel e. (h) Output characteristics (h) panel e. (h) panel e. (h) Output characteristics (h) panel e. (h) panel e. (h) Output characteristics (h) panel e. (h) panel e. (h) Output ch

We have carried out systematic study of the electrical performance of the SN-TFTs as basic components for macroelectronic integrated circuits. Figure 2 panels c and d are the transfer characteristics ( $I_D - V_G$ ) of the SN-TFTs using 95% (Figure 2c) and 98% (Figure 2d) semiconducting nanotubes with various channel lengths (4, 10, 20, 50, and 100 µm) and 100 µm channel width plotted in logarithm scale. All the curves are measured at  $V_D = 1$  V. From the figures, we can have the following straightforward observations. (1) Devices from both

The on-current ( $I_{on}$ ) at  $V_D = 1$  V,  $V_G = -10$  V is measured to be 35.6  $\mu$ A, corresponding to an on-current density ( $I_{on}/W$ ) of 0.356  $\mu$ A/ $\mu$ m. The transconductance ( $g_m$ ) extracted from the maximum slope of the transfer characteristics is 4.6  $\mu$ S and the on/off ratio is 482. For the 98% semiconducting nanotube SN-TFT (Figure 2g), the channel length is 100  $\mu$ m and channel width is 50  $\mu$ m. The on-current density is 0.058  $\mu$ A/ $\mu$ m, transconductance is 0.53  $\mu$ S and on/off ratio is 3  $\times$  10<sup>5</sup>. The corresponding output characteristics ( $I_D - V_D$ ) of these two

nanotube samples

show p-type field-effect behavior and much higher on/off ratio compared with the devices fabricated using unsorted nanotubes,

which typically exhibit an on/off ratio of

around 2-3. (2) As the

device channel length

increases, the on/off ra-

tio increases while the

on-current decreases.

Especially for the SN-

TFTs with 95% semi-

the on/off ratio im-

proves significantly

10<sup>4</sup> as the channel

conducting nanotubes,

from around 10 to over

length increases from 4

to 100 µm. (3) The de-

vices using 98% semi-

conducting nanotubes

exhibit better on/off ra-

tios but lower on-

current than the de-

vices using 95% semi-

conducting nanotubes.

Figure 2 panels e

and g exhibit the trans-

fer characteristics (red,

linear scale; green, log

scale) and  $g_{\rm m} - V_{\rm G}$  char-

acteristics (blue) of two

95% and 98% semicon-

measured at  $V_{\rm D} = 1$  V.

For the 95% semicon-

ducting nanotube SN-

width of the device are

TFT (Figure 2e), the

channel length and

$L = 50 \ \mu m$  and  $W = 100 \ \mu m$ , respectively.

typical SN-TFTs using

ducting nanotubes

ARTICLE

SN-TFTs are plotted in Figure 2 panels f and h, respectively. The output characteristics appear to be very linear under small  $V_D$  biases, indicating that ohmic contacts are formed between the metal electrodes and the nanotubes. Under more negative  $V_D$  biases, the devices exhibit saturation behavior, indicating nice fieldeffect operation.

On the basis of the transconductance, we can further extract the device mobility of the SN-TFTs. Under  $V_D = 1 \text{ V}$ , devices operate in the triode region, so the device mobility can be calculated from the following equation,

$$\mu_{\text{device}} = \frac{L}{V_{\text{D}}\mathsf{C}_{\text{ox}}W} \frac{\mathsf{d}I_{\text{d}}}{\mathsf{d}V_{\text{g}}} = \frac{L}{V_{\text{D}}\mathsf{C}_{\text{ox}}} \frac{g_{\text{m}}}{W} \tag{1}$$

where *L* and *W* are the device channel length and width,  $V_D = 1$  V, and  $C_{ox}$  is the gate capacitance per unit area. The capacitance is calculated by considering the electrostatic coupling between nanotubes using the following equation,<sup>34,35</sup>

$$C_{\rm ox} = \left\{ C_{\rm Q}^{-1} + \frac{1}{2\pi\varepsilon_0\varepsilon_{\rm ox}} \ln\left[\frac{\Lambda_0}{R}\frac{\sinh(2\pi t_{\rm ox}/\Lambda_0)}{\pi}\right] \right\}^{-1} \Lambda_0^{-1}$$

(2)

where  $1/\Lambda_0$  stands for the density of nanotubes and is measured to be around 10 tubes/ $\mu$ m,  $C_Q = 4.0 \times 10^{-10}$ F/m is the quantum capacitance of nanotubes and the value is taken from a previous report,<sup>36</sup>  $t_{ox} = 50$  nm is the thickness of the dielectric layer, R = 1.2 nm is the radius of nanotubes, and  $\varepsilon_0\varepsilon_{ox} = 3.9 \times 8.85 \times 10^{-14}$

F/cm is the dielectric constant at the interface where the nanotubes are placed. On the basis of eq 2, one can find that  $C_{ox} = 3.46 \times 10^{-8}$  F/cm.<sup>2</sup> Using this  $C_{ox}$  value and on the basis of the device geometry and normalized transconductance  $g_m/W$ , the device mobility is calculated to be 67 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for the 95% semiconducting nanotube SN-TFT, and 31 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> for the 98% semiconducting nanotube SN-TFT.

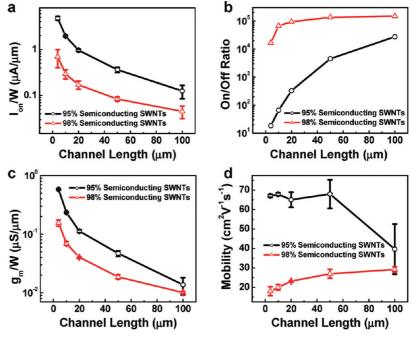

To get a more comprehensive understanding, we compare the key device performance metrics such as oncurrent density, on/off ratio, transconductance, and mobility for SN-TFTs based on separated nanotubes with different purities of semiconducting nanotubes. Figure 3 summarizes the results after the measurement of 175 SN-TFTs with various channel lengths, channel widths, and different semiconducting nanotube purities. Out of the devices measured, 100 of them are fabricated on 95% semiconducting nanotubes, and 75 of them are fabricated on 98% semiconducting nanotubes.

Figure 3a exhibits the normalized on-current densities  $(I_{on}/W)$  of the transistors with various channel lengths measured at  $V_D = 1$  V and  $V_G = -10$  V, showing that the on-current density is approximately inversely proportional to the channel length for both 95% and 98% semiconducting nanotubes. The highest oncurrent density from SN-TFTs using 95% semiconducting nanotubes is measured to be 5.2  $\mu$ A/ $\mu$ m and the highest on-current density from SN-TFTs using 98% semiconducting nanotubes is measured to be 1.0  $\mu$ A/  $\mu$ m. Both values are achieved in devices with  $L = 4 \mu$ m. Comparing the data for transistors using 95% and 98% semiconducting nanotubes, one can easily find that the average on-current density of 95% semiconducting nanotubes is higher than the on-current density of 98% semiconducting nanotubes by a factor of 3-7 at all device channel lengths measured. The difference in the on-current density can be attributed to the difference in nanotube lengths. For instance, the average length for the 95% semiconducting nanotubes is approximately 0.97  $\mu$ m, while the average length for the 98% semiconducting nanotubes is about 0.81 µm. For transistors of similar channel length, using longer nanotubes would lead to less nanotube-nanotube junctions, and consequently better performance. Besides, for devices using both 95% and 98% semiconducting nanotubes, the measurement results exhibit very small error bar, indicating the highly uniform nature of the

Figure 3. Statistical study of 175 SN-TFTs using separated nanotubes with 95% and 98% semiconducting nanotubes, as well as comparison of key device performance metrics. Plot of (a) current density ( $I_{on}/W$ ), (b) average on/off ratio ( $I_{on}/I_{off}$ ), (c) normalized transconductance ( $g_m/W$ ), and (d) device mobility ( $\mu_{device}$ ) versus channel length for TFTs fabricated on separated nanotubes with 95% (black trace) and 98% (red trace) semiconducting nanotubes.

SN-TFTs. More information about the uniformity of the SN-TFT device performance metrics ( $I_{on}/W$ , on/off ratio, mobility) is discussed in the Supporting Information (Figure S1).

For SN-TFTs fabricated using separated nanotubes with different purities of semiconducting nanotubes, besides the difference in on-current density discussed previously, the other major difference is expected to be the on/off ratio and the difference is explained in Figure 3b. First of all, as the channel length increases, the average on/off ratio of SN-TFTs using both 95% and 98% semiconducting nanotubes increases. This can be explained by the decrease in the probability of percolative transport through metallic nanotube networks as the device channel length increases. On the other hand, SN-TFTs with 98% semiconducting nanotubes have much higher on/off ratio compared with SN-TFTs with 95% semiconducting nanotubes, especially at small channel lengths, which can be naturally attributed to the small percentage of metallic nanotubes. For SN-TFTs with 95% semiconducting nanotubes, the on/off ratio improves significantly from around 10 to above  $10^4$  as the channel length increases from 4 to 100  $\mu$ m. In contrast, for the SN-TFTs 98% semiconducting nanotubes, the device on/off ratio stays above 10<sup>4</sup> at all channel lengths.

Interestingly, the data shown in Figure 3a,b reveal a trade-off between drive-current and on/off ratio. By using separated nanotubes with higher purity of semiconducting nanotubes, on one hand, it can help to achieve sufficient on/off ratio with smaller channel length, thus smaller device area; on the other hand, since higher purity requires more ultracentrifugation which will give rise to shorter nanotube length, it can cause more nanotube percolation and hurt the overall devices performance such as on-current density discussed previously and mobility as will be discussed below.

Besides the on-current density and on/off ratio, there are two more important figures of merit for SN-TFTs, which are device transconductance ( $g_m$ ) and mobility ( $\mu_{device}$ ). The normalized transconductance ( $g_m/W$ ) of devices with various channel lengths are characterized and are plotted in Figure 3c;  $g_m$  is extracted from the maximum slope of the transfer characteristics measured at  $V_D = 1$  V, and is normalized to device channel width. From the figure, one can find that as channel length increases,  $g_m/W$  decreases. This is because  $g_m/W$  is also inversely proportional to channel length. Moreover, similar to  $I_{on}/W$ , the SN-TFTs using 95% semiconducting nanotubes also exhibit better performance in terms of  $g_m/W$  compared with SN-TFTs using 98% semiconducting nanotubes.

Using the data for the normalized transconductance plotted in Figure 3c and eq 1, we can calculate the devices mobility of the SN-TFT, and the data is plotted in Figure 3d. Interestingly, the device mobility of the SN-TFTs with 95% and 98% semiconducting nanotubes follows different trends. For the SN-TFTs with 95% semiconducting nanotubes, the device mobility decreases as channel length increases, while for the SN-TFTs with 98% semiconducting nanotubes, the device mobility increases as channel length increases. The reason for the decreasing trend of the SN-TFTs using 95% semiconducting nanotubes is attributed to the percolative transport through the nanotube network. As the device channel length increases from a value comparable to the nanotube length to a much larger value, there are significantly more tube-to-tube junctions introduced into the conduction path, causing the device mobility to decrease.<sup>32</sup> On the other hand, it is not yet clear why the SN-TFTs using 98% semiconducting nanotubes show increasing trend in the device mobility as the channel length increases, and this is currently under further investigation in our group. Another important point is that devices using 95% semiconducting nanotubes exhibit higher mobilities than devices using 98% semiconducting nanotubes. Besides the difference in the purity of semiconducting nanotubes, other factors such as nanotube length, density of nanotube network, etc. also play a role in determining the ultimate electrical performance of the SN-TFTs, resulting in the difference between the 95% and 98% semiconducting nanotubes in terms of device mobility, as well as on-current density, transconductance, and on/off ratio discussed before. The reason is that the difference in nanotube length and density can affect the nanotube percolation network, changing the amount of tube-totube junctions, and the probability of metallic conduction path formation between the source and drain electrodes. Numerical simulations have been performed by our group and other groups<sup>32,37–39</sup> to fully assess such effect on the performance of nanotube TFTs.

Our ability to fabricate high performance, uniform, high on/off ratio SN-TFTs enable us to further explore their applications in digital integrated circuits. We have already discussed the trade-off between on-current and on/off ratio for different purities of semiconducting nanotubes, and we choose to use the separated nanotubes with 98% semiconducting nanotubes for the digital integrated circuit fabrication. The reason is that for digital application, it is desirable to have large switching, preferably rail-to-rail, in order to achieve large noise margin. More importantly, the off-state current has to be low to reduce the static power consumption. Therefore, it is more important for the transistors to have a large on/off ratio rather than high on-current. For SN-TFTs with 98% semiconducting nanotubes, At all channel lengths measured, more than 95% of the devices exhibit on/off ratio higher than 10<sup>4</sup>. This amount of on/off ratio is large enough for most kinds of integrated circuit applications.

For the proof of concept purpose, we demonstrate the basic digital functional blocks such as inverter,

AGNANO

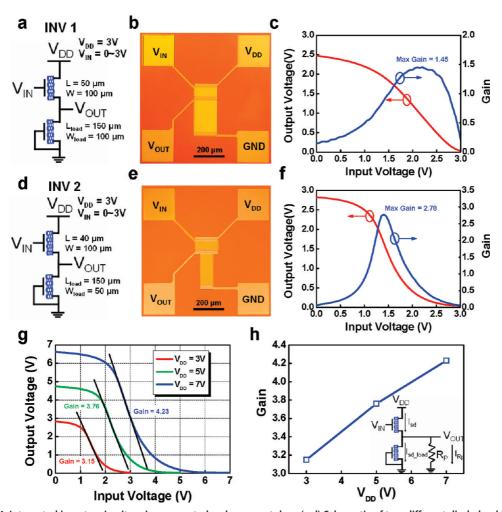

Figure 4. Integrated inverter circuits using separated carbon nanotubes. (a,d) Schematic of two different diode-load inverters using SN-TFTs with different device dimensions. (b,e) Optical microscope images of these two corresponding inverters. (c,f) Inverter voltage transfer characteristic (red trace) and voltage gain (blue trace) of these two corresponding inverters. Both inverters work with a  $V_{DD}$  of 3 V and exhibit symmetric input/output behavior. (g) Inverter voltage transfer characteristics measured at different supply voltages ( $V_{DD}$ ). (h) Curve showing the dependence between the inverter voltage gain and supply voltage. Inset: schematic of the circuit with parasitic resistance at the output node.

2-input NAND, and NOR using SN-TFTs. The fabrication process of these integrated circuits is discussed in the methods section. We start with the inverter design and find that the highly uniform nature of the SN-TFTs allows us to optimize the circuit performance using the conventional silicon transistor circuit design theory. As an example, for the diode-load inverter investigated in Figure 4, the output impedance looking into the source of the diode-connected SN-TFTs is  $1/q_{m \text{ load}}$ , and the voltage gain of the inverter is given by  $A_V = g_m R_{out} \approx$  $g_{\rm m}/g_{\rm m}$  load. For transistors operating in the saturation region, the transconductance can be calculated by  $g_m$ =  $(2\mu_p C_{ox}(W/L)I_{sd})^{1/2}$ , where  $\mu_p$  is the mobility of the devices,  $C_{ox}$  is the gate capacitance per unit area, and  $I_{sd}$ is the source-drain current of the transistor. Considering that the current flowing through the switching transistor  $(I_{sd})$  is equal to current flowing through the diodeconnected transistor ( $I_{sd_{load}}$ ), we can find the gain of the diode-load inverter to be equal to

$$A_{\rm V} = \frac{g_{\rm m}}{g_{\rm m\_load}} = \frac{\sqrt{2\mu_{\rm p}C_{\rm ox}(W/L)I_{\rm sd}}}{\sqrt{2\mu_{\rm p}C_{\rm ox}(W_{\rm load}/L_{\rm load})I_{\rm sd\_load}}} = \sqrt{\frac{W}{W_{\rm load}}\frac{L_{\rm load}}{L}}$$

(3)

where W, L,  $W_{load}$ , and  $L_{load}$ , are the channel width, channel length for the switching transistor, and channel width, channel length for the diode-load transistor, respectively.

The schematics of two diode-load inverters with different geometries used in this study are shown in Figure 4a,d. By design, inverter 1 has W = 100, L = 50,  $W_{load} = 100$ ,  $L_{load} = 150 \mu m$ ; while inverter 2 has W = 100, L = 40,  $W_{load} = 50$ , and  $L_{load} = 150 \mu m$ . The corresponding optical microscope images of these two inverters are shown in Figure 4 panels b and e, respectively. In the circuit, one transistor is acting as the switching transistor and is connected between the supply voltage  $V_{DD}$  and the output, and the other transistor is config-

www.acsnano.org

VOL. 4 • NO. 12 • 7123-7132 • 2010

7130

SNANO

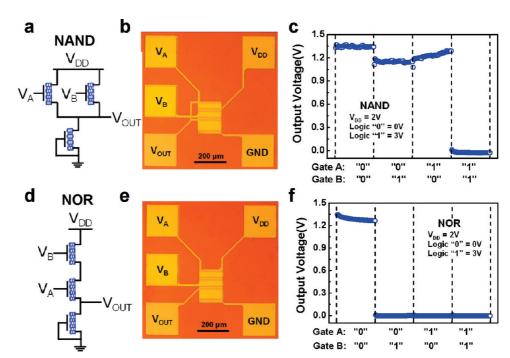

Figure 5. Integrated 2-input NAND and NOR circuits using separated carbon nanotubes. (a,d) Schematic of diode-load 2-input NAND and NOR circuits using SN-TFTs. (b,e) Optical microscope images of the corresponding NAND and NOR circuits. (c,f) Output characteristics of the corresponding NAND and NOR circuits. The supply voltages for both circuits are  $V_{DD} = 2$  V. Input voltages of 3 and 0 V are treated as logic "1" and "0", respectively.

ured as a diode-load and is connected between the output and ground. The inverters are characterized by sweeping input voltage  $V_{IN}$  and measure the output voltage  $V_{OUT}$ . The corresponding inverter voltage transfer characteristics are plotted in Figure 4 panels c and f, respectively. For the measurement,  $V_{DD}$  is biased at 3 V and  $V_{IN}$  is swept between 0 and 3 V. Measurements reveal that for both inverters, as input voltages increase from 0 to 3 V, output voltages decrease from 3 to 0 V, meaning that they are functioning correctly as logic inverters. The maximum voltage gain measured is 1.45 for inverter 1 and 2.78 for inverter 2. According to the conventional diode-load inverter circuit design equation discussed before (eq 3) and the device dimensions, we have  $A_{V1} = \sqrt{3} \approx 1.73$  for inverter 1 and  $A_{V2} = \sqrt{7.5} \approx$ 2.74 for inverter 2. This means that our measurement results are consistent with the conventional circuit design theory, and by simply changing the dimension of the switching and load transistors in the layout design, we can achieve inverters with different voltage gains.

Another very important merit for the inverters using SN-TFTs is that they offer symmetric input/output behavior, meaning that both input and output are operating under the same voltage range  $(0-3 \text{ V} \text{ in this}}$ case). This character is important for single power supply voltage operation and is crucial for cascading logic blocks for larger scale integration where the output of the preceding logic block needs to be able to drive the ensuing logic block directly.

The relationship between the gain of the inverters and the power supply voltage is also studied, and the voltage transfer characteristics for an inverter measured

under different  $V_{DD}$  are shown in Figure 4g. From the figure, we find that the inverter keeps showing symmetric input/output behavior under all supply voltages. Besides, if we plot the voltage gain versus V<sub>DD</sub> (Figure 4h), we see a monotonic increase in maximum voltage gain as the  $V_{DD}$  increases. It is worth noting that for the diode-load inverters, the voltage gain is ideally independent of  $V_{DD}$  as shown in eq 3. The reason we see the increasing trend is due to the finite input impedance of the measurement instrument (HP 4156B in this case). Since the input impedance of the measurement instrument  $(R_{\rm P})$  is not infinitely large compared with the output impedance of the SN-TFT used in the inverters, the instrument draws some amount of current ( $I_{Rp}$ ). As  $V_{DD}$ increases, the output DC level at the maximum voltage gain increases, causing I<sub>Rp</sub> to increase. From Kirchhoff current law, we have  $I_{sd} = I_{sd\_load} + I_{Rp}$ , so as  $V_{DD}$  increases, I<sub>sd load</sub> is getting smaller and smaller compared with I<sub>sd</sub>. Furthermore, based on eq 3, the inverter voltage gain is proportional to  $(I_{sd}/I_{sd\_load})^{1/2}$ , this explains why the voltage gain increases as the power supply voltage increases.

In addition to inverters, more sophisticated circuits such as 2-input NAND and NOR have also been demonstrated. Figure 5 shows the schematics (Figure 5a,d), optical microscope images (Figure 5b,e) and output characteristics (Figure 5c,f) of the NAND and NOR, respectively. Both logic blocks employ a diode-connected SN-TFT in the pull-down network similar to the inverters and they are both operated with a  $V_{DD}$  of 2 V. The 3 V and 0 V applied on gate A and B are treated as logic "1" and "0'', respectively. For the NAND, the output is "1" when either one of the two inputs is "0" (Figure 5c), while for the NOR, the output is "0" when either one of the two inputs is "1" (Figure 5f). These output characteristics confirm that our circuits are realizing the logic function correctly. With the combination of these basic logic blocks, more sophisticated logic circuits which require cascading multiple stages of logic gates can be readily constructed, and the work is currently ongoing in our group.

In conclusion, we report the progress on the application of separated nanotube thin-film transistors for macroelectronic integrated circuits, including progress on the direct comparison of key performance metrics of devices using separated nanotubes with 95% and 98% semiconducting nanotubes, and the demonstration of integrated digital logic blocks with symmetric input/ output behavior. We have revealed the trade-off between the on-current density and on/off ratio for the SN-TFT device optimization, and the optimized SN-TFTs with excellent yield, current density, mobility, and on/ off ratio have been used to demonstrate integrated digital logic circuits such as inverter, NAND, and NOR. Moreover, we have demonstrated that it is possible to tune the circuit performance by simply changing the device dimensions in the layout design, and the experimental results are in accordance with conventional silicon field-effect transistor circuit design theory. Our work represents significant advance in the separated nanotube thin-film electronics, which solves the problem of coexistence of both metallic and semiconducting nanotubes in the state-of-the-art nanotube transistor fabrication techniques, and can provide guide to future research on SN-TFT based integrated circuits.

# ARTICLE

## **METHODS**

Separated Nanotube Deposition. Aminopropyltriethoxy silane (APTES) is used to functionalize the Si/SiO<sub>2</sub> surface to form amineterminated monolayer. This is done by immersing the Si/SiO<sub>2</sub> substrate into diluted APTES solution (1% APTES in isopropyl alcohol (IPA)) for 10 min. The sample is then rinsed with IPA, blown dry thoroughly, and then immersed into the commercially available 0.01 mg/mL separated nanotube solution with 95% or 98% semiconducting nanotubes (NanoIntegris Inc.) for 20 min, after which uniform nanotube networks are formed on top of the substrates.

**Back-Gated SN-TFT Fabrication.** SiO<sub>2</sub> with a thickness of 50 nm is used to act as the back-gate dielectric. The source and drain electrodes are patterned by photolithography, and 5 Å Ti and 60 nm Pd are deposited followed by the lift-off process to form the source and drain metal contacts. Finally, since the separated nanotube thin film covers the entire wafer, in order to achieve accurate channel length and width, and to remove the possible leakage in the devices, one more step of photolithography plus O<sub>2</sub> plasma is used to remove the unwanted nanotubes outside the device channel region.

Individual-Gated SN-TFT and Integrated Circuit Fabrication. First, Ti/Au back-gate electrodes are patterned by photolithography and lift-off process. 50 nm Al<sub>2</sub>O<sub>3</sub> high- $\kappa$  dielectric and 5 nm SiO<sub>2</sub> are then deposited on top of the Ti/Au back-gate by atomic layer deposition and e-beam evaporation, respectively. Contact vias are then patterned using photolithography, and buffered oxide etch (BOE) is used to remove the oxide layer in the contact vias to allow the interconnection between the gate and drain of the transistor to form the diode-connected load transistor. The separated nanotube thin-film is then deposited on the dielectric layer using the method discussed above, and the rest of the fabrication steps including the source/drain electrodes patterning and unwanted nanotube etching are the same as the back-gate transistor fabrication discussed previously.

Acknowledgment. We acknowledge financial support from the National Science Foundation (CCF-0726815 and CCF-0702204). We thank Professor Mark Hersam of Northwestern University and Mr. Elliott Garlock and Dr. Nathan Yoder of Nanointegris for valuable discussions.

Supporting Information Available: Uniformity of the SN-TFTs using 95% and 98% semiconducting nanotubes. This material is available free of charge via the Internet at http://pubs.acs.org.

## **REFERENCES AND NOTES**

- Bockrath, M.; Cobden, D.; McEuen, P.; Chopra, N.; Zettl, A.; Thess, A.; Smalley, R. Single-Electron Transport in Ropes of Carbon Nanotubes. *Science* **1997**, *275*, 1922–1925.

- 2. Wildoer, J.; Venema, L.; Rinzler, A.; Smalley, R.; Dekker, C.

Electronic Structure of Atomically Resolved Carbon Nanotubes. *Nature* **1998**, *391*, 59–62.

- Odom, T.; Huang, J.; Kim, P.; Lieber, C. Atomic Structure and Electronic Properties of Single-Walled Carbon Nanotubes. *Nature* 1998, 391, 62–64.

- 4. Tans, S.; Verschueren, A.; Dekker, C. Room-Temperature Transistor Based on a Single Carbon Nanotube. *Nature* **1998**, *393*, 49–52.

- Martel, R.; Schmidt, T.; Shea, H. R.; Hertel, T.; Avouris, P. Single- and Multiwall Carbon Nanotube Field-Effect Transistors. *Appl. Phys. Lett.* **1998**, *73*, 2447–2449.

- Javey, A.; Guo, J.; Wang, Q.; Lundstrom, M.; Dai, H. Ballistic Carbon Nanotube Field-Effect Transistors. *Nature* 2003, 424, 654–657.

- Dulrkop, T.; Getty, S. A.; Cobas, E.; Fuhrer, M. S. Extraordinary Mobility in Semiconducting Carbon Nanotubes. *Nano Lett.* **2003**, *4*, 35–39.

- Zhou, X.; Park, J. Y.; Huang, S.; Liu, J.; McEuen, P. L. Band Structure, Phonon Scattering, and the Performance Limit of Single-Walled Carbon Nanotube Transistors. *Phys. Rev. Lett.* 2005, *95*, 146805.

- Bachtold, A.; Hadley, P.; Nakanishi, T.; Dekker, C. Logic Circuits with Carbon Nanotube Transistors. *Science* 2001, 294, 1317–1320.

- Derycke, V.; Martel, R.; Appenzeller, J.; Avouris, P. Carbon Nanotube Inter- and Intramolecular Logic Gates. *Nano Lett.* 2001, 1, 453–456.

- Liu, X.; Lee, C.; Han, J.; Zhou, C. Carbon Nanotube Field-Effect Inverters. Appl. Phys. Lett. 2001, 79, 3329–3331.

- Javey, A.; Wang, Q.; Ural, A.; Li, Y.; Dai, H. Carbon Nanotube Transistor Arrays for Multistage Complementary Logic and Ring Oscillators. *Nano Lett.* **2002**, *2*, 929–932.

- Chen, Z.; Appenzeller, J.; Lin, Y.; Oakley, J. S.; Rinzler, A. G.; Tang, J.; Wind, S. J.; Solomon, P. M.; Avouris, P. An Integrated Logic Circuit Assembled on a Single Carbon Nanotube. *Science* **2006**, *311*, 1735.

- Snow, E. S.; Novak, J. P.; Campbell, P. M.; Park, D. Random Networks of Carbon Nanotubes as an Electronic Material. *Appl. Phys. Lett.* **2003**, *82*, 2145–2147.

- Snow, E. S.; Campbell, P. M.; Ancona, M. G.; Novak, J. P. High-Mobility Carbon-Nanotube Thin-Film Transistors on a Polymeric Substrate. *Appl. Phys. Lett.* **2005**, *86*, 033105-1-033105-3.

- Artukovic, E.; Kaempgen, M.; Hecht, D. S.; Roth, S.; Gruner, G. Transparent and Flexible Carbon Nanotube Transistors. *Nano Lett.* 2005, *5*, 757–760.

- Hu, L.; Hecht, D. S.; Gruner, G. Percolation in Transparent and Conducting Carbon Nanotube Networks. *Nano Lett.* 2004, 4, 2513–2517.

- 18. Zhang, D.; Ryu, K.; Liu, X.; Polikarpov, E.; Ly, J.; Tompson,

- VOL. 4 NO. 12 7123-7132 2010

M. E.; Zhou, C. Transparent, Conductive, and Flexible Carbon Nanotube Films and Their Application in Organic Light-Emitting Diodes. *Nano Lett.* **2006**, *6*, 1880–1886.

- Ishikawa, F.; Chang, H.; Ryu, K.; Chen, P.; Badmaev, A.; De Arco Gomez, L.; Shen, G.; Zhou, C. Transparent Electronics Based on Transfer Printed Aligned Carbon Nanotubes on Rigid and Flexible Substrates. ACS Nano 2009, 3, 73–79.

- Cao, Q.; Rogers, J. A. Ultrathin Films of Single-Walled Carbon Nanotubes for Electronics and Sensors: A Review of Fundamental and Applied Aspects. *Adv. Mater.* 2008, 21, 29–53.

- Cao, Q.; Kim, H. S.; Pimparkar, N.; Kulkarni, J. P.; Wang, C.; Shim, M.; Roy, K.; Alam, M. A.; Rogers, J. A. Medium-Scale Carbon Nanotube Thin-Film Integrated Circuits on Flexible Plastic Substrates. *Nature* **2008**, *454*, 495–500.

- 22. Street, R. A., Ed. *Technology and Applications of Amorphous Silicon*; Springer: Berlin, 2000.

- 23. Ucjikoga, S. Low-Temperature Polycrystalline Silicon Thin-Film Transistor Technologies for System-on-Glass Displays. *MRS Bull.* **2002**, *27*, 881–886.

- Snell, A. J.; Mackenzie, K. D.; Spear, W. E.; LeComber, P. G.; Hughes, A. J. Application of Amorphous Silicon Field Effect Transistors in Addressable Liquid Crystal Display Panels. *Appl. Phys. A: Mater. Sci. Process.* **1981**, *24*, 357–362.

- 25. Dimitrakopoulos, C. D.; Mascaro, D. J. Organic Thin-Film Transistors: A Review of Recent Advances. *IBM J. Res. Dev.* **2001**, *45*, 11–27.

- Forrest, S. R. The Path to Ubiquitous and Low-Cost Organic Electronic Appliances on Plastic. *Nature* 2004, 428, 911–918.

- Gelinck, G. H.; Edzer, H.; Huitema, A.; Van Veenendaal, E.; Cantatore, E.; Schrijnemakers, L.; Van Der Putten, J. B. P. H.; Geuns, T. C. T.; De Leeuw, D. M.; *et al.* Flexible Active-Matrix Displays and Shift Registers Based on Solution-Processed Organic Transistors. *Nat. Mater.* **2004**, *3*, 106–110.

- Klauk, H.; Halik, M.; Zschieschang, U.; Eder, F.; Rohde, D.; Schmid, G.; Dehm, C. Flexible Organic Complementary Circuits. *IEEE Trans. Electron Devices* 2005, *52*, 618–622.

- Arnold, M. S.; Green, A. A.; Hulvat, J. F.; Stupp, S. I.; Hersam, M. C. Sorting Carbon Nanotubes by Electronic Structure Using Density Differentiation. *Nat. Nanotechnol.* 2006, 1, 60–65.

- Arnold, M. S.; Stupp, S. I.; Hersam, M. C. Enrichment of Single-Walled Carbon Nanotubes by Diameter in Density Gradients. *Nano Lett.* 2005, *5*, 713–718.

- Engel, M.; Small, J. P.; Steiner, M.; Freitag, M.; Green, A. A.; Hersam, M. C.; Avouris, P. Thin Film Nanotube Transistors Based on Self-Assembled, Aligned, Semiconducting Carbon Nanotube Arrays. ACS Nano 2008, 2, 2445–2452.

- Wang, C.; Zhang, J; Ryu, K.; Badmaev, A.; Gomez, L.; Zhou, C. Wafer-Scale Fabrication of Separated Carbon Nanotube Thin-Film Transistors for Display Applications. *Nano Lett.* 2009, 9, 4285–4291.

- LeMieux, M. C.; Roberts, M.; Barman, S.; Jin, Y. W.; Kim, J. M.; Bao, Z. Self-Sorted, Aligned Nanotube Networks for Thin-Film Transistors. *Science* 2008, *321*, 101–104.

- Kang, S. J.; Kocabas, C.; Ozel, T.; Shim, M.; Pimparkar, N.; Alam, M. A.; Rotkin, S. V.; Rogers, J. A. High-Performance Electronics Using Dense, Perfectly Aligned Arrays of Single-Walled Carbon Nanotubes. *Nature Nanotechnol.* 2007, 2, 230–236.

- Cao, Q.; Xia, M.; Kocabas, C.; Shim, M.; Rogers, J. A.; Rotkin, S. V. Gate Capacitance Coupling of Singled-Walled Carbon Nanotube Thin-Film Transistors. *Appl. Phys. Lett.* 2007, *90*, 023516-1–023516-3.

- Rosenblatt, S.; Yaish, Y.; Park, J.; Gore, J.; Sazonova, V.; McEuen, P. L. High Performance Electrolyte Gated Carbon Nanotube Transistors. *Nano Lett.* **2002**, *2*, 869–872.

- Pimparkar, N.; Kocabas, C.; Kang, S. J.; Rogers, J. A.; Alam, M. A. Limits of Performance Gain of Aligned CNT Over Randomized Network: Theoretical Predictions and Experimental Validation. *Electron Device Lett.* **2007**, *28*, 593–595.

- 38. Kocabas, C.; Pimparkar, N.; Yesilyurt, O.; Alam, M. A.;

Rogers, J. A. Experimental and Theoretical Studies of Transport through Large Scale, Partially Aligned Arrays of Single-Walled Carbon Nanotubes in Thin Film Type Transistors. *Nano Lett.* **2007**, *7*, 1195–1202.

Pimparkar, N.; Cao, Q.; Kumar, S.; Murthy, J. Y.; Rogers, J. A.; Alam, M. A. Current–Voltage Characteristics of Long-Channel Nanobundle Thin-Film Transistors: A "Bottom-Up" Perspective. *Electron Device Lett.* 2007, 28, 157–160.